■量子ドット

- 量子ドット作成-トップダウンとボトムアップの二つのアプローチ

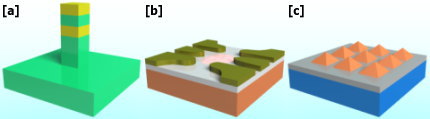

様々な方法でつくった量子ドット。[a]はリソグラフィーなどトップダウンで製作。[b]はトップダウンの技術で電極を作り、仮想的に量子ドットを作ったもの。[c]はskモードで自己形成したボトムアップのアプローチ。 |

量子ドットの産業的な大量生成には、主に二つのアプローチがある。まず一つ目に、これまで半導体産業で用いられてきた技術を利用することで、バルク材料を切ったり削ったりするという「トップダウン(top down)」的なアプローチがある。もう一つは、固体表面で結晶成長させるときにひずみの力を利用して、量子ドットを自己形成させるという「ボトムアップ(bottom up)」的なアプローチがある。後者の方はここ数年で展望の開けてきた感じがあり、まだ未発達の段階にあるが、これまでの半導体産業の製造方法に大きなパラダイム変化を与えるとして、今後の研究のゆくえが期待されている。

トップダウン的アプローチ

この基本的なスタイルは、二次元的な量子井戸を縦横に切り分けることで、もしくは一次元の量子細線を切り分けることで、零次元の量子ドットをつくろうというものだ。

まずはCVD(Chemical Vapor Deposition,化学気相成長)などによって、10nm程度の量子井戸層をもったSOI(Silicon

On Insulater、絶縁膜上にシリコン層)膜をつくる。

この面と平行にレジストポリマーを付着させ、電子線リソグラフィー(電子ビームリソグラフィ、EBL;Electron

Beam Lithography)で取り除く。光を用いたフォトリソグラフィーでは、光の波長の大きさの限界によって、最小加工寸法が100nm程度になってしまうので、量子ドットの作成には向かない。しかし、電子線リソグラフィーによる加工は時間がかかりすぎるという欠点もある。

こうして一部レジストを取り除いたあとで、金属を薄膜蒸着させる。このあとレジストを除去すると、先にレジストが取り除かれた部分の金属片だけが取り除かれる。

最後に、イオンエッチングによって金属で保護された以外の量子井戸層を取り除く。こうして量子ドットが出来あがる。[図a]

なお他にも、金属片を4つ作って電極とし、印加することで電極に囲まれた量子井戸の領域に電子が蓄えられて、仮想的な量子ドットを作るという方法もある。この方法では、電圧の程度によって量子ドットの大きさなどを自由に変えられることから、量子ドットの性質を研究するのに向いていると考えられている。[図b]

(半導体産業の様々な技術は解体真書「ICチップが出来るまで」を参照)

ボトムアップ的アプローチ

固体表面での結晶の自己形成モード。薄膜を形成する原子(M)と基板の化学結合力をDsm、MとMの化学結合力をDmmとする。このとき、Dmm>DsmならVWモードで、Dsm>DmmならSMモード。SKモードはSとMの格子定数のミスマッチとDsm>>Dmmのときに起こるとされている。 |

半導体産業で薄膜形成を行うとき、基板と薄膜の格子定数の一致が大前提になってくる。格子定数とは結晶の原子と原子の距離についてもので、格子定数が大きく異なるものどうしで薄膜形成を行うと均一な平面構造をもった薄膜が形成できない。こうなると欠損が生じて、電子の移動度が下がったりして、半導体デバイスとしては使い物にならなくなってしまう。

しかし、量子ドットの場合は逆の発想で、格子定数のミスマッチを利用して、ひずみの力で島状構造をつくろうというものである。特にこの結晶成長のモードは「SK(Stranski-Krastanov)モード」と呼ばれている。

このSKモードの例として有名なものは、Si膜上にGe(ゲルマニウム)を蒸着させてピラミッド状のナノクラスターが生成するものだろう。[図c]

しかし最近では、蒸着するGeの量や温度によって、量子ドットではなくナノワイヤが形成されることもわかっている。とくにSi上にエルビウムシリサイド(ErSi2)を成長させた場合、非常にきれいなナノワイヤが形成されることから、ボトムアップのチップ製造法にいかせないかと研究が行われている。(例えばHP(ヒューレット・パッカード)社は有機分子を用いた分子スイッチとこのナノワイヤで、デバイス素子をつくった。詳しくは「HP社の示した分子コンピュータへのロードマップ」を参照)

SKモードで成長させた様々な結晶のSTMイメージ(着色あり)

http://www.hpl.hp.com/research/qsr/gallery/gallery.html HP社 http://www.hpl.hp.com/research/qsr/gallery/gallery.html HP社

現時点では、この結晶成長モードを支配する要素が完全に分かっているわけではないが、これは量子ドットに限らず、今後のエレクトロニクス分野全域に大きな影響を与えるものとして、大いに注目したい。

|

|